# 4-77-21

## MUTING IC

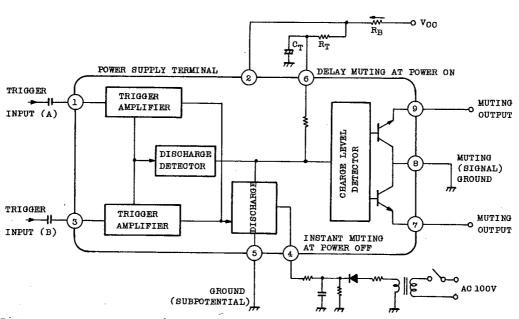

TA7324P is developed for muting the popping sound made at power of one-off receivers, preamplifiers, main amplifiers, and other electric audio equipment as well as the noise made at changeover of switches.

- . To mute the popping noise made in the case of receiving frequency or changeover of signal source of tuners.

- . Delay muting at power ON.

- . Instant muting at power OFF.

- . Only a single timing capacitor and a very few external parts are provided.

- . Either positive or negative pulse is applicable to the input trigger. The terminals consist of the high sensitive input terminal (sensitive level of 120mV) and the low sensitive input terminal (sensitive level of +700mV)

- . The operating power supply current is 5mA (Min.) available for portable sets.

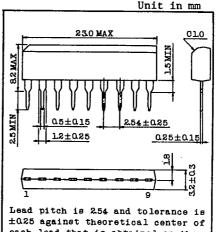

each lead that is obtained on the basis of No.1 lead.

| JEDEC   |       |  |

|---------|-------|--|

| TOSHIBA | 89A-P |  |

## **BLOCK DIAGRAM**

02E 17098

D

T-77-21

**TA7324P**

MAXIMUM RATINGS (Ta=25°C)

| CHARACTERISTIC                              | SYMBOL           | RATING                       | UNIT |  |

|---------------------------------------------|------------------|------------------------------|------|--|

| Supply Voltage (V2-5)(Notel                 | V <sub>2-5</sub> | 3.4                          | v    |  |

| Supply Current ( $^{\mathrm{I}}$ 2) (Note2) |                  | 20                           | mA   |  |

| Power Dissipation (Note 3)                  | PD               | 500                          | mW   |  |

| Operating Temperature                       | Topr             | -20 ∿ 75                     | °C   |  |

| Storage Temperature                         | Tstg             | <b>-</b> 55 <sup>∿</sup> 150 | °C   |  |

Note 1. In case of constant voltage source.

Note 2. In case of constant current source.

Note 3. Derated above Ta=25°C in the proportion of  $4\mbox{mW}/\mbox{°C}$

The input voltage at the trigger terminal is GND-V $_{\rm BE}$ ( $\stackrel{\sim}{=}0.7\rm{V}$ )<input voltage < V $_{2-5}$ +V $_{\rm BE}$ . When trigger terminals A and B are applied, must be set the operating supply current value from 5mA to 15mA.

ELECTRICAL CHARACTERISTICS (Ta=25°C,  $v_{CC}$ =18V,  $R_B$ =1.5k $\Omega$ )

| C.I                                           | 1100 (                |                      | *CC ±0*  | , KB-T. 2KW)    |       |       |       |      |

|-----------------------------------------------|-----------------------|----------------------|----------|-----------------|-------|-------|-------|------|

| CHARACTERISTEC                                | SYMBOL                | TEST<br>CIR-<br>CUIT | TEST     | CONDITION       | MIN.  | TYP.  | MAX.  | נומט |

| Supply Terminal Voltage                       | V <sub>2-5</sub>      | 1                    | Note 4   | ICC=20mA(CONST) | 3.4   | 3.6   | 3.8   | v    |

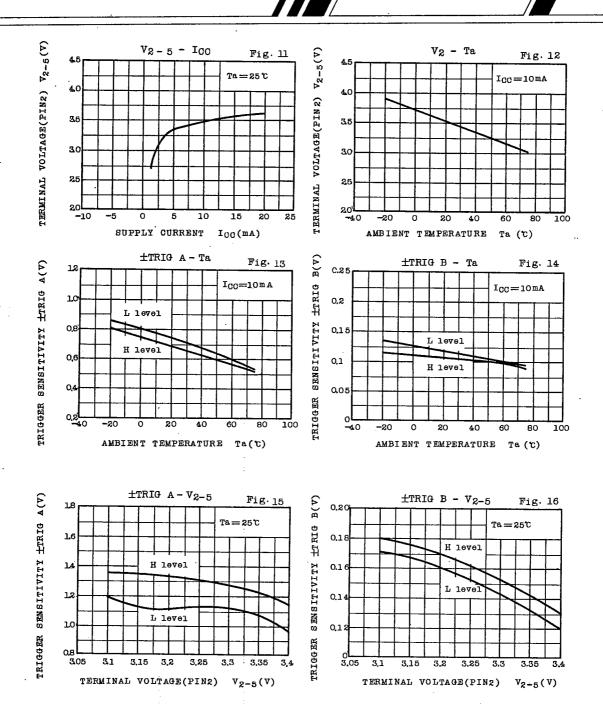

| Trigger Sensitivity(A) $V_1$                  | ±TRIGA                | 1                    | Note 6   |                 | ±0.5  | ±0.7  | ±0.9  | v    |

| Trigger Sencitivity(B) V <sub>3</sub>         | ±TRIGB                | 1                    | Note 7   |                 | ±0.09 | ±0.12 | ±0.15 | v    |

| Trigger Sensitivity(A) $I_1$                  | t(I TRIG-A)           | 1                    | Note 6   |                 | -     | ±20   | ±60   | uA   |

|                                               | t(I TRIG-B)           | 1                    | Note 7   |                 | _     | ±10   | ±30   | uA   |

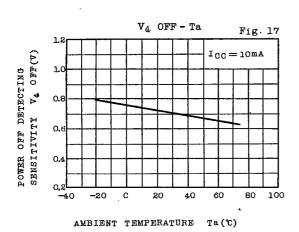

| Detecting sensitivity at power OFF V4         | V <sub>4</sub> OFF    | 1                    | Note 8   |                 | _     | 0.75  | 1.0   | v    |

| Detecting current at power OFF                | I4 OFF                | 1                    | Note 8   |                 |       | 6     | -     | uA   |

| Output Saturation Voltage at muting ON V7, V9 | V <sub>CE</sub> (sat) |                      | N-4-0    | <del></del>     | -     | 18    | 40    | mV   |

| Max. Sink Current I7, I9                      | Imax                  | _                    | Note 9   |                 | 1.4   | 1.6   | _     | mA.  |

| Terminal Voltage (Pin 1)                      | v <sub>1</sub>        |                      | Note 5   |                 | _     | 1.5   | _     | V    |

| Terminal Voltage (Pin 2)                      | v <sub>2</sub>        | 1                    |          | 3.2             | 3.5   | 3,6   | v     |      |

| Terminal Voltage (Pin 3)                      | <b>v</b> <sub>3</sub> |                      |          |                 |       | 1.4   |       | V    |

| Terminal Voltage (Pin 6)                      |                       |                      | Muting ( | OFF             | 2.6   | 2.7   | 2.8   | v    |

| Muting Attenuation                            | ATT                   |                      | Note 10  |                 | 45    | 50    |       | dB   |

| Muting Time at Power ON                       | M.T                   | 2                    |          |                 | -     | 1.8   | -     | sec  |

**TA7324P**

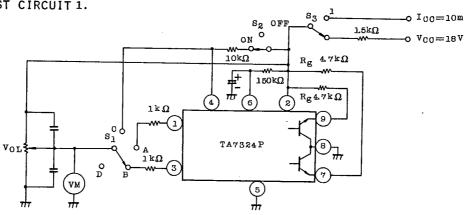

TEST CIRCUIT 1.

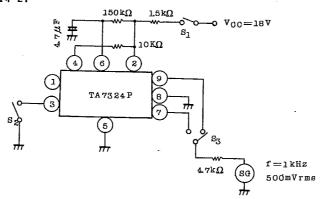

TEST CIRCUIT 2.

Note 4) Supply terminal Voltage  $(V_{2-5})$

$$S_1 \rightarrow D$$

,  $S_2 \rightarrow ON$ ,  $S_3 \rightarrow 1$  (SW positions)

Read the voltage of pin 2 at  $I_{\mbox{CC}}=20\mbox{mA}$ .

Note 5) Terminal voltage  $(v_1, v_2, v_3, v_6)$

$$S_1 \rightarrow D$$

,  $S_2 \rightarrow ON$ ,  $S_3 \rightarrow V$  (SW positions)

9097247 TOSHIBA. ELECTRONIC

02E 17100 D

T-77-21

**TA7324P**

Read each terminal voltage at the above SW position.

Note 6) Trigger sensitivity (A), Trigger current (A) < TRIG-A, +(I-TRIG-A)>

$$S_1 \rightarrow A$$

,  $S_2 \rightarrow ON$ ,  $S_3 \rightarrow V$  (SW position)

Turn VOL gradually to increase the indication of VM from OV. In this case, pin 9 and pin 7 of the muting output terminal are at L level (about OV when output transistor is ON.).

As the value of VM is increased, pin 9 and pin 7 are turned from "L" level to "H" level at a certain point (about 3.5mA when output transistor is OFF. In this case, if the value of VM is  $V_{\rm ML}(A)$  the negative trigger sensitivity (A) is given by the following equation:

Negative trigger sensitivity (A), -TRIG-A=V1-VMH(A)

If, after obtaining of the negative trigger sensitivity, the value of VM is further increased, pin 9 and pin 7 are re-turned from "H" level to "L" level.

In this case, if the indicating value of VM is  $V_{\text{MH}(A)}$ , the positive trigger sentivitity (A) is given as follows:

To measure the trigger current  $\pm$ (I-TRIG-A), read the current of pin 1 at the measuring time of the  $V_{\rm ML(A)}$  and  $V_{\rm MH(A)}$  described above.

Note 7) Trigger sensitivity (B), trigger current (B) <+TRIG-B, +(I-TRIG-B)>

$$S_1 \rightarrow B$$

,  $S_2 \rightarrow ON$ ,  $S_3 \rightarrow V$  (SW position)

Measuring method is the same as mentioned in Note 5.

Negative trigger sensitivity, -TRIG-B=V3-VML(B)

Positive trigger sensitivity, -TRIG-B=VMH(B)-V3

9097247 TOSHIBA. ELECTRONIC

02E 17101

T-77-21

**TA7324P**

Note 8) Detection sensitivity and current at power OFF ( $V_{L}$ OFF,  $I_{L}$ OFF)

$$S_1 \rightarrow C$$

,  $S_2 \rightarrow OFF$ ,  $S_3 \rightarrow V$

(SW position)

Turn VOL gradually to increase the indicating value of VM from OV. When pin 9 and pin 7 of the muting output are turned from "L" level to "H" level, the value of VM comes to  $V_4$ . In this case, the current of pin 4 is I4 OFF.

Note 9) Saturation voltage and maximum sink current at muting ON  $(v_{CE(sat)}, i_{Cmax})$

$$S_1$$

A or B,  $S_2$  ON,  $S_3$  V (SW position)

Measure the voltage and current of pin 9 and pin 7 when indicating value of VM is set to OV. (Set  $R_g$ =0 at measuring the current.)

Note 10) Muting attenuation and muting time at power ON (ATT, MT)

In the measuring circuit 2, the time from the instant when  ${\rm S}_1$  is ON (while  ${\rm S}_2$  remains OFF) and  ${\rm V}_{\rm CC}$  is applied to the circuit, to the moment when pin 9 and pin 7 are turned from "L" level to "H" level is taken as the muting time MT.

Measure the AC voltage at pin 9 or pin 7 with  $\rm S_1$  remains ON. In addition, turn  $\rm S_2$  ON, and measure the AC voltage at pin 9 or pin 7.

Muting attenuation ATT=20 log

AC voltage at pin 7 (9) at  $^{\rm S2}$  OFF AC voltage at pin 7 (9) at  $^{\rm S2}$  ON

T-77-21

**TA7324P**

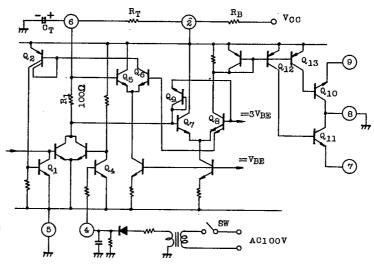

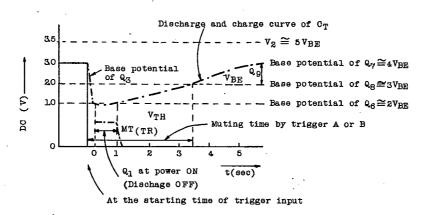

# CHARGE AND DISCHARGE LEVEL DETECTION

A built-in trigger amplifier is included in TA7324P for responding either to positive or negative pulse. In the trigger amplifier, two amplifiers are mounted in parallel; one is responding at a small level, while the other is responding at a large level. Both amplifiers are coupled to the discharge

Fig.1 Charge and Discharge Level

Equivalent Circuit

level detector circuit as shown Fig. 1 respectively.

The discharge level detector circuit forms a flip-flop discharge circuit. The circuit is designed so that the trigger pulse width to discharge circuit may be maintained beyond constant width to discharge fully the charge of CT (Capacitor for muting and charging operation) even when the smaller width pulse is given to the trigger amplifier.

Charge operation and muting operation are described as follows:

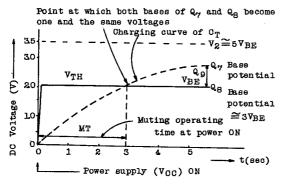

# 1. OPERATION AT POWER (VCC) ON (REFER TO FIG.2)

As soon as the power supply (V<sub>CC</sub>) is ON, C<sub>T</sub> starts to be charged through R<sub>T</sub> and the potential V<sub>6</sub> on pin 6 rises gradually, in this case, Q<sub>8</sub> remains conductive till the base potential of Q<sub>7</sub> becomes equal to or more than the base potential (3 V<sub>BE</sub> $\stackrel{\text{\tiny $\cong$}}{=}2.1$ V) of Q<sub>8</sub> and the muting operation is carried on by putting the muting output T<sub>R</sub> Q<sub>10</sub> and Q<sub>11</sub> to ON position.

When the base potential of  $Q_7$  rises higher than that of  $Q_8$ , the  $Q_8$ ,  $Q_{10}$  and  $Q_{11}$  are OFF to release the muting operation. CT charge stops at such a level as the base potential of  $Q_7$  is  $V_{\rm BE}$  ( $ilde{\approx}0.7V$ ) higher than that of Q8.

Fig. 2 Operating Potential of Each Part at Power ON

- Q1 : For discharge stop

- Q2 : For Q1 drive

- Q3 and Q3: For discharge

- Q4: For muting operation at power OFF

- Q5 and Q6 : Discharge level detecting differenctial

- $Q_7$  and  $Q_8$ : For charge level detection and muting output stage drive

- Q9 : For charge level limit  $Q_{10}$  and  $Q_{11}$ : Output  $T_R$  for muting

# 2. MUTING OPERATION BY TRIGGER A OR B (REFER TO FIG.3)

When a pulse from the trigger amplifier comes in Q3 base, Q3 is ON to discharge the charge from  $C_{\mathrm{T}}$  through  $R_{\mathrm{1}} (=100\Omega)$ . When the discharge level of  $C_{T}(Q_{7}$  base potential) drops lower than the base potential of  $0_8$  (3VBE=2.1V), the  $0_8$ ,  $0_{10}$ , and  $0_{11}$  are turned ON to start the muting operation in which  $R_1$  is designed for accelerating the speed to start muting operation.

When more discharge is carried on from  $C_{T}$ , if  $Q_{5}$  base potential drops lower than  $Q_6$  base potential (2 $V_{BE}$ =1.4V), the  $Q_6$ ,  $Q_2$ , and  $Q_1$ are turned ON to stop discharging by shortening  $\mathbf{Q}_3$  base. ( $\mathbf{Q}_1$  acts also as a flip-flop operating reverse potential.)

When discharging stops, charging to  $C_{_{\rm T}}$  starts through  $R_{_{\rm T}}$ . When the base potential of  $Q_5$  rises higher than that of  $Q_6$ , the  $Q_6$ ,  $Q_2$ , and  $Q_1$  are turned OFF.

ELECTRONIC

9097247 TOSHIBA.

TA7324P

When  $\rm C_T^{}$  is more charged, the base potential of  $\rm Q_7^{}$  rises higher than that of  $\rm Q_8^{}$  , and the  $\rm Q_8^{}$  ,  $\rm Q_{10}^{}$  , and  $\rm Q_{11}^{}$  are turned OFF to release the muting.

Fig. 3 Respective Operating Potentials at Mating by Trigger (A) or (B)

# 3. MUTING AT POWER OFF

When the power supply is ON, rectification from AC makes  $\mathbf{Q}_4$  ON and  $\mathbf{Q}_3$  OFF.

When AC is OFF,  $\mathbf{Q}_4$  is OFF and  $\mathbf{Q}_3^1$  is ON to dischage  $\mathbf{C}_T$  for stating muting operation.

D

02E 17105

T-77-21

**TA7324P**

# APPLICATION

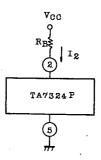

1 SUFFLY VOLTAGE (V  $_{2-5}$ ) AND SUFFLY CURRENT (I $_2$ )

TA7324P contains a regulated power supply. Therefore, as shown in Fig. 4, the voltage is applied to pin 2 through the resistor  $R_{\rm B}$ . The supply current  $I_2$  is, in this case, adjusted to about 10mA by difining the value of  $R_{\rm B}$ .

According to  $V_{2-5}$  to  $I_2$  characteristics shown in Fig. 4 Adding bias to Fig. 1, when  $I_2$  = 10mA,  $V_{2-5}$   $\stackrel{=}{=}$  3.5V is given. Pin 2

Thus,  $R_B = \frac{V_{CC} - V_{2-5}}{10}$  (k $\Omega$ )

For muting operation  $\rm V_{2-5}\gtrsim 2.8V$  is required. As shown in Fig.1 if the current of  $\rm I_2\gtrsim 3mA$  is flown, the muting function starts operating.

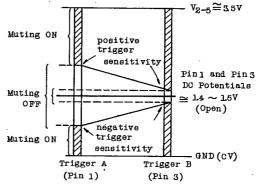

# 2. TRIGGER SENSITIVITY

, Trigger sensitivity means the absolute value in the difference between the trigger terminal voltage at the start and the open voltage of trigger terminal. (Refer to Fig. 5.)

Trigger current is the value of current flowing into or from the trigger terminal at start of triggering.

Fig. 5 Trigger Level

In TA7324P, the circuit is designed for discharging securely the timing capacitor even if a trigger of extremely narrow width is applied to the trigger input terminal. Consequently, the trigger is applied to even the input of pulse width less than lms, so that an erroneous operation may be caused when by a hair-like pulse is applied

to the trigger input terminal from the power supply or other sources. To prevent such erroneous operation, an integrated circuit of CR may be required to be provided to the input. In addition, trigger snesitivity varies according to temperature and voltage of  $\mathbf{V}_{2-5}$ ; therefore, such variation should be considered before designing. Trigger terminal impedance is  $15k\Omega{\sim}25k\Omega$  at start of triggering.  $I_2=5\sim15\text{mA}$  is recommended for pin 1 or pin 3 because muting may not be restored after triggering to mute if  $I_2=15mA$  or more is applied.

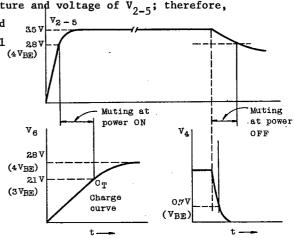

Fig. 6 Muting Operation at Power ON - OFF

3. MUTING AT POWER ON/OFF (Refer to Fig. 6)

#### 3.1 MUTING AT POWER ON

Muting at power ON continues till  $\rm V_{2-5}$  is over about. 2.8V (4V  $_{\rm BE}$ ),  $\rm Q_{12}$  and  $\rm Q_{13}$  are turned ON, the timing capacitor  $\mathbf{C}_{\mathbf{T}}$  is charged, and the base potential of  $\mathbf{Q}_{7}$ rises to about 2.1V (5 $V_{\rm BE}$ ). Therefore, early rise is recommended for  $V_{2-5}$  potential.

#### 3.2 MUTING AT POWER OFF

Muting at power OFF starts operating by decreasing the detecting terminal (pin 4) at OFF to about 0.7V or less (making Q4 OFF.) Therefore, such a signal as is more than 0.7V in normal operation but turned to less than 0.7V instantly at (35V) power OFF, is required to be made.

Muting at power OFF starts operating at the time when pin 4 potential becomes less than 0.7V and continues till  $V_{2-5}$  becomes 2.8V or less. Therefore, the slow falling of  $V_{2-5}$  is more effective.

Fig. 7 Lengthening Way of Muting Time

TA7324P

The detecting terminal at power OFF (pin 4) is available for trigger input; however, it is recommended that this terminal be linearly triggered as much as possible, because a narrower width . pulse may miss ample discharge from the timing capacitor.

#### 4. MUTING TIME

Muting time at power ON and casused by trigger is decided by the timing  $C_T$  and  $R_T$ . With the consideration for  $Q_5$  and  $Q_7$  base currents, the following are roughly given:

Muting time at power ON :  $MT_{(ON)} = 1.3R_TC_T$

Muting time by trigger :  $MT_{(TR)} = 0.45R_TC_T$

Here, if muting time is lengthened by setting  $\mathbf{R}_{\mathbf{T}}\mathbf{C}_{\mathbf{T}}$  time constant larger, distorted waves asymmetrical with respect to top and bottom may be originated by the slow speed of wave rise at muting OFF. Experiment tells that MT<sub>(ON)</sub>=1.4sec ( $R_T$ =220k $\Omega$  and  $C_T$ =4.7 $\mu$ F) or less has brought a good result.

When MT (ON) is required especially to be made longer, a method of applying the trigger terminal as shown in Fig. 7 and another method of giving a signal of slow rise to the detecting terminal at power OFF. (pin 4) are considered. To activate a continuous muting, the DC voltage to make muting ON should be applied to trigger A or B, or the voltage of the detecting terminal at power OFF (pin 4) should be decreased to make  $Q_{\Lambda}$  OFF.

Fig. 8 Muting Output

9097247 TOSHIBA.

ELECTRONIC

02E 17108 T-77-21

$\mathbf{D}^{\prime}$

ΓA7324P

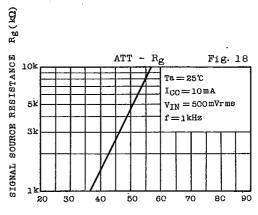

#### 5. SINGNAL LEVEL FOR MUTING AND ATTENUATION

Since peak value (half wave) and attenuation of signal for muting are decided according to the following conditions, the value of  $R_{\sigma}$  is properly required for operation.

o At muting ON, V<sub>IN(peak)</sub>=Rg. I<sub>max</sub>

$I_{\mbox{max}}$  is minimum value of maximum sink current.

- o At muting OFF, peak value and attenuation are decided by emitterbase reverse voltage of  $Q_{10(011)}$ , and the equation,  $V_{IN(peak)} \leq 5V$ , is given.

- o Let  $\mathbf{Q}_{10\,\mathrm{(Q11)}}$  saturating resistance be  $\mathbf{R}_{\mathbf{S}}$ , muting attenuation is given by

Muting attenuation: ATT=-20log  $R_S/R_g$   $R_S = (V_{CE(sat)}/I_{max})$

- (1) Utilization of voltage variation added to the variable capacitance diode

- (2) Utilization of voltage variation caused by station indicator LED

== AUDIO LINEAR IC==

D

**TA7324P**

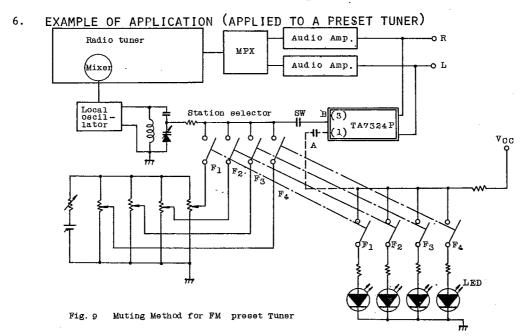

In case of an FM preset tuner as shown in Fig. 9, station selection from  $\mathbf{F}_1$  to  $\mathbf{F}_2$  by the preset station selector switch provides a drastic variation to the voltage applied to variable capacitance diode.

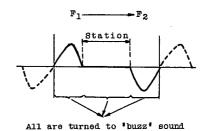

Accordingly, all of the detector Fig. 10 \*Buzz\* Sound in DC voltage variation traced in and Present Type out the FM"S"curve and noise between stations as shown in Fig. 10 come out as "buzz" sound.

o In case of the above FM preset tuner equipped with a non-shorting type switch for station selection and the station indicator LED (or an indicator lamp), only LED voltage detection can operate muting securely by using the terminal 1 of TA7324P, that is, the trigger A, as shown by the dotted line in Fig. 9.

For example, in case of presetting from  $F_1$  to  $F_2$ , after SW of  $F_1$  turned OFF, SW of  $F_2$  becomes ON; therefore, detection of switch OFF of  $F_1$  permits the muting operation to be performed.

o Even in case of using a shorting type switch, if the contact of indicator SW linked with the preset SW is securely ON several milli second ahead, the muting operation can be performed by voltage variation originated at LED ON. If the shorting type switch cannot securely make the other switch ON, the muting starts operating by detecting the voltage variation of variable capacitance by applying the terminal 3 of TA7324P, the trigger B, as shown by the solid line in Fig. 9.

However, in case where  $F_1$  and  $F_2$  are the same station or close stations at reception each other, no muting can be operated. (Variation is within several mV of variable capacitance diode voltage.)

TA7324P

9097247 TOSHIBA. ELECTRONIC

02E 17111 D T-77-21

**TA7324P**